What Is the Post (Power-on Self Test), and What Can Be Done to Troubleshoot This Process?

Typical POST screen. (AMI BIOS)

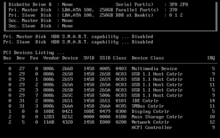

Summary screen subsequently POST and before booting an operating system (AMI BIOS)

A power-on cocky-test (Mail service) is a process performed past firmware or software routines immediately later on a computer or other digital electronic device is powered on.[1]

This article mainly deals with POSTs on personal computers, but many other embedded systems such equally those in major appliances, avionics, communications, or medical equipment also have self-test routines which are automatically invoked at power-on.[ii]

The results of the Mail service may exist displayed on a console that is part of the device, output to an external device, or stored for future retrieval by a diagnostic tool. Since a self-exam might discover that the system'south usual human being-readable display is non-functional, an indicator lamp or a speaker may exist provided to bear witness error codes every bit a sequence of flashes or beeps. In improver to running tests, the POST process may also ready the initial state of the device from firmware.

In the case of a computer, the Post routines are part of a device's pre-boot sequence; if they complete successfully, the bootstrap loader code is invoked to load an operating system.

IBM-compatible PC Post [edit]

In IBM PC compatible computers, the chief duties of POST are handled by the BIOS/UEFI, which may paw some of these duties to other programs designed to initialize very specific peripheral devices, notably for video and SCSI initialization. These other duty-specific programs are mostly known collectively as option ROMs or individually as the video BIOS, SCSI BIOS, etc.

The chief duties of the primary BIOS during Post are as follows:

- verify CPU registers

- verify the integrity of the BIOS code itself

- verify some basic components similar DMA, timer, interrupt controller

- initialize, size, and verify system chief memory

- initialize BIOS

- pass command to other specialized extension BIOSes (if installed)

- place, organize, and select which devices are available for booting

The functions higher up are served past the Postal service in all BIOS versions back to the very first. In later on BIOS versions, Postal service volition also:

- initialize chipset

- detect, initialize, and catalog all arrangement buses and devices

- provide a user interface for organisation's configuration

- construct whatever system environment is required past the target operating system

(In early BIOSes, POST did not organize or select boot devices, it simply identified floppy or hard disks, which the system would endeavor to boot in that order, always.)

The BIOS begins its POST when the CPU is reset. The beginning retentivity location the CPU tries to execute is known every bit the reset vector. In the case of a hard reboot, the northbridge will direct this code fetch (request) to the BIOS located on the system flash retention. For a warm kick, the BIOS will be located in the proper place in RAM and the northbridge will direct the reset vector call to the RAM. (In earlier PC systems, earlier chipsets were standard, the BIOS ROM would be located at an address range that included the reset vector, and BIOS ran directly out of ROM. This is why the motherboard BIOS ROM is in segment F000 in the conventional memory map.)

During the POST menses of a contemporary BIOS, one of the get-go things a BIOS should do is make up one's mind the reason information technology is executing. For a common cold boot, for example, it may need to execute all of its functionality. If, nonetheless, the system supports power saving or quick boot methods, the BIOS may be able to circumvent the standard POST device discovery, and simply plan the devices from a preloaded organization device table.

The Mail flow for the PC has developed from a very simple, straightforward process to one that is complex and convoluted. During the Postal service, the BIOS must integrate a plethora of competing, evolving, and fifty-fifty mutually exclusive standards and initiatives for the matrix of hardware and OSes the PC is expected to back up, although at most simply unproblematic memory tests and the setup screen are displayed.

In earlier BIOSes, upward to effectually the plow of the millennium, the Post would perform a thorough test of all devices, including a consummate memory test. This blueprint by IBM was modeled subsequently their larger (e.grand. mainframe) systems, which would perform a consummate hardware test as part of their cold-outset process. As the PC platform evolved into more of a commodity consumer device, the mainframe- and minicomputer-inspired high-reliability features such as parity retentivity and the thorough memory test in every POST were dropped from most models. The exponential growth of PC memory sizes, driven by the as exponential drop in memory prices, was also a factor in this, every bit the duration of a retention test using a given CPU is straight proportional to the memory size.

The original IBM PC could exist equipped with as piffling equally 16 KB of RAM and typically had between 64 and 640 KB; depending on the amount of equipped memory, the reckoner's iv.77 MHz 8088 required betwixt five seconds and 1.5 minutes to complete the POST and there was no fashion to skip information technology. Beginning with the IBM XT, a retention count was displayed during POST instead of a blank screen.[iii] A modern PC with a bus rate of around 1 GHz and a 32-scrap autobus might be 2000x or even 5000x faster, simply it might accept more than 3 GB of retentivity—5000x more than. With people being more concerned with boot times now than in the 1980s, the 30 to 60 2nd retention examination adds undesirable delay for a do good of confidence that is non perceived to exist worth that cost by most users. Virtually clone PC BIOSes allowed the user to skip the POST RAM bank check by pressing a key, and more modern machines oft performed no RAM test at all unless it was enabled via the BIOS setup. In addition, mod DRAM is significantly more than reliable than DRAM was in the 1980s.

As role of the starting sequence the POST routines may display a prompt to the user for a key printing to access built-in setup functions of the BIOS. This allows the user to set various options particular to the female parent board before the operating system is loaded. If no key is pressed, the POST will proceed on to the kicking sequence required to load the installed operating arrangement.

Many mod BIOS and UEFI implementations show a manufacturers logo during Mail service and hide the classic text screens unless an error occurs. The text screen tin can often be enabled in the BIOS settings by disabling the "Serenity Boot" option.

Progress and error reporting [edit]

BIOS Mail service carte for PCI double-decker.

Professional BIOS POST card for PCI bus.

Two POST 7-segment displays integrated on a estimator motherboard

The original IBM BIOS fabricated Post diagnostic information available by outputting a number to I/O port 0x80 (a screen display was not possible with some failure modes). Both progress indication and mistake codes were generated; in the case of a failure which did not generate a lawmaking, the code of the last successful functioning was bachelor to assistance in diagnosing the trouble. Using a logic analyzer or a dedicated Mail service card—an interface card that shows port 0x80 output on a pocket-sized display—a technician could determine the origin of the trouble. One time an operating organization is running on the computer the code displayed by such a board may become meaningless, since some OSes, e.g. Linux, utilise port 0x80 for I/O timing operations. The actual numeric codes for the possible stages and error conditions differ from one BIOS supplier to another. Codes for different BIOS versions from a single supplier may also vary, although many codes remain unchanged in unlike versions.

Subsequently BIOSes used a sequence of beeps from the motherboard-fastened PC speaker (if present and working) to point error codes. Some vendors adult proprietary variants or enhancements, such equally MSI's D-Subclass. Mail service beep codes vary from manufacturer to manufacturer.

Information on numeric and beep codes is bachelor from manufacturers of BIOSes and motherboards. In that location are websites which collect codes for many BIOSes.[4]

Original IBM POST beep codes [edit]

| Beeps | Significant |

|---|---|

| i curt beep | Normal POST – arrangement is OK |

| two brusque beeps | Postal service fault – error code shown on screen |

| No beep | Power supply, system lath problem, asunder CPU, or disconnected speaker |

| Continuous beep | Power supply, system lath, RAM or keyboard problem |

| Repeating short beeps | Power supply, organisation board or keyboard trouble |

| 1 long, 1 short beep | System board problem |

| 1 long, 2 brusk beeps | Display adapter trouble (MDA, CGA) |

| 1 long, 3 short beeps | Enhanced Graphics Adapter problem (EGA) |

| three long beeps | 3270 keyboard card fault |

Mail service AMI BIOS beep codes [edit]

| Beeps | Meaning |

|---|---|

| i | Memory refresh timer error |

| 2 | Parity error in base of operations memory (first 64 KiB block) |

| iii | Base memory read/write examination error |

| 4 | Motherboard timer not operational (check all PSU to MB connectors seated) |

| 5 | Processor failure |

| 6 | 8042 Gate A20 exam fault (cannot switch to protected mode) |

| 7 | General exception error (processor exception interrupt error) |

| viii | Display memory fault (system video adapter) |

| nine | AMI BIOS ROM checksum fix |

| 10 | CMOS shutdown annals read/write fix |

| 11 | Cache memory test failed |

| continuous beeping | Motherboard does non discover a RAM module (continuous beeping) |

Reference: "AMIBIOS8 Check Point and Beep Code List Version 2.0 - June 10, 2008" (PDF). Archived from the original (PDF) on 2015-08-07.

POST beep codes on CompTIA A+ certification exam [edit]

These Post beep codes are covered specifically on the CompTIA A+ Test:

| Beeps | Meaning |

|---|---|

| Steady, short beeps | Power supply may be bad |

| Long continuous beep tone | Memory failure |

| Steady, long beeps | Power supply bad |

| No beep | Power supply bad, organisation non plugged in, or ability not turned on |

| No beep | If everything seems to exist operation correctly in that location may exist a problem with the 'beeper' itself. The system will normally beep 1 short beep. |

| One long, ii brusque beeps | Video card failure |

IBM Mail diagnostic lawmaking descriptions [edit]

| Code | Meaning |

|---|---|

| 100–199 | System boards |

| 200–299 | Memory |

| 300–399 | Keyboard |

| 400–499 | Monochrome brandish |

| 500–599 | Color/graphics display |

| 600–699 | Floppy-disk drive or adapter |

| 700–799 | Math coprocessor |

| 900–999 | Parallel printer port |

| chiliad–1099 | Alternate printer adapter |

| 1100–1299 | Asynchronous communication device, adapter, or port |

| 1300–1399 | Game port |

| 1400–1499 | Color/graphics printer |

| 1500–1599 | Synchronous communication device, adapter, or port |

| 1700–1799 | Hard drive or adapter (or both) |

| 1800–1899 | Expansion unit of measurement (XT) |

| 2000–2199 | Bisynchronous communication adapter |

| 2400–2599 | EGA system-board video (MCA) |

| 3000–3199 | LAN adapter |

| 4800–4999 | Internal modem |

| 7000–7099 | Phoenix BIOS fries |

| 7300–7399 | 3.five-inch disk drive |

| 8900–8999 | MIDI adapter |

| 11200–11299 | SCSI adapter |

| 21000–21099 | SCSI fixed disk and controller |

| 21500–21599 | SCSI CD-ROM system |

Macintosh POST [edit]

Apple tree's Macintosh computers also perform a Mail service after a common cold boot. In the outcome of a fatal fault, the Mac will not brand its startup chime.

Old Earth Macs (until 1998) [edit]

Macs made after 1987 but prior to 1998, upon failing the Postal service, will immediately halt with a "death chinkle", which is a sound that varies past model; it can be a beep, a car crash audio, the sound of shattering glass, a short musical tone, or more. On the screen, if working, will be the Sad Mac icon, along with two hexadecimal strings, which can be used to identify the problem. Macs made prior to 1987 crashed silently with the hexadecimal string and a Lamentable Mac icon.

New World Macs (1998–1999) [edit]

When Apple introduced the iMac in 1998, it was a radical departure from other Macs of the time. The iMac began the production of New Earth Macs, every bit they are called; New Globe Macs, such equally the iMac, Power Macintosh G3 (Blue & White), Power Mac G4 (PCI Graphics), PowerBook G3 (statuary keyboard), and PowerBook G3 (FireWire), load the Mac OS ROM from the hard bulldoze. In the result of an error, but not a fatal hardware error, they brandish the aforementioned screen as seen when holding ⌘ Control+⌥ Pick+O+F at startup simply with the error bulletin instead of the "0 >" prompt. In the event of a fatal hardware error, they requite these beeps:[v]

| Beeps | Meaning |

|---|---|

| i | No RAM installed/detected |

| 2 | Incompatible RAM type installed (for example, EDO) |

| 3 | No RAM banks passed memory testing |

| 4 | Bad checksum for the residuum of the boot ROM |

| v | Bad checksum for the ROM boot block |

New World Macs (1999 onward) [edit]

The beep codes were revised in October 1999.[half-dozen] In add-on, on some models, the power LED would flash in cadence.

| Beeps | Meaning |

|---|---|

| i | No RAM installed/detected |

| 2 | Incompatible RAM types |

| 3 | No good banks |

| four | No skilful boot images in the boot ROM, bad sys config block, or both |

| five | Processor is not usable |

Intel-based Macs [edit]

With the introduction of Intel-based Macs with EFI-based firmware, the startup tones were changed again.[7]

| Tones | Meaning |

|---|---|

| One tone, repeating every five seconds | No RAM installed/detected |

| 3 successive tones followed by a repeating five-2d break | Incompatible RAM types |

| One long tone while the power button is held down | EFI ROM update in progress |

| 3 long tones, three short tones, iii long tones | EFI ROM corruption detected, ROM recovery in process |

Macs with the T2 security fleck don't have EFI ROM tones[7]

Amiga POST [edit]

Amiga historical line of computers, from A1000 to 4000 present an interesting Mail sequence that prompts the user with a sequence of flashing screens of different colors (rather than audible beeps every bit in other systems) to prove if diverse hardware Mail service tests were correct or else if they failed:

Mail service sequence of Amiga [edit]

The Amiga system performs the post-obit steps at boot:

- Delays beginning the tests a fraction of a second to allow the hardware to stabilize.

- Jumps to ROM code in diagnostic carte du jour (if establish)

- Disables and clears all DMA and interrupts.

- Turns on the screen.

- Checks the full general hardware configuration. If the screen remains a light greyness color and the tests continue, the hardware is OK. If an error occurs, the organisation halts.

- Performs checksum test on ROMs.

If the system fails the ROM test, the screen display turns ruby-red and the organisation halts.

Sequence for all main Amiga models [edit]

Almost all Amiga models nowadays the same colour sequence when turned on: black screen, night greyness, light grey color screens filling all monitor screen in a rapid sequence (Amigas taken up normally 2, or at to the lowest degree max 3 seconds to plough on and kicking).[8]

Colour screens scheme [edit]

| Color | Pregnant | |

|---|---|---|

| Red | Bad ROM[8] | |

| Yellow | CPU Exception Before Bootstrap Code is Loaded[8] | |

| Green | Bad Chip RAM or neglect of Agnus Chip (bank check seating of Agnus) | |

| Blackness | No CPU | |

| White | Expansion passed exam successfully | |

| Grey | Turn on | |

| Constant white | Failure of CPU | |

| Royal | Return from InitCode()[eight] | |

Sequence for A4000 [edit]

Correct tests color sequence scheme [edit]

A4000 presents only a low-cal grey screen during its boot time (it only occurs in 2 or max 3 seconds)

- Light Greyness

- = Initial hardware configuration tests passed

- = Initial system software tests passed

- = Final initialization test passed

Failed tests color scheme [edit]

| Color | Meaning | |

|---|---|---|

| Cherry-red | ROM Mistake - Reset or supervene upon | |

| Green | Fleck RAM error (reset AGNUS and re-test) | |

| Blue | Custom Chip(due south) Error | |

| Xanthous | 68000 detected error before software trapped it (GURU) | |

Amiga keyboard LED error signals [edit]

The keyboards of historical Amiga models are not proprietary every bit it happened in early on calculator ages, but more than pragmatically it was based on international standard ANSI/ISO 8859-one. The keyboard itself was an intelligent device and had its ain processor and 4 kilobytes of RAM for keeping a buffer of the sequence of keys that were being pressed, thus tin communicate with the user if a mistake is found by flashing its main LED in sequence:

| Blinks | Meaning |

|---|---|

| i | ROM checksum failure |

| 2 | RAM test failed |

| 3 | Watchdog timer failed |

| four | A shortcut exists betwixt two row lines or one of the seven special keys (non implemented) |

See also [edit]

- POST carte

- Serial presence observe

References [edit]

- ^ "How BIOS Works". flint.cs.yale.edu . Retrieved 2021-ten-22 .

- ^ "Hardware Diagnostics and Ability on Cocky Tests". www.eventhelix.com . Retrieved 2021-10-22 .

- ^ Williams, Gregg (January 1982). "A Closer Look at the IBM Personal Calculator". BYTE. p. 36. Retrieved 19 Oct 2013.

- ^ "Post Code Master - PC BIOS Ability On Self Test POST Codes & Diagnostic Beep Codes". Archived from the original on June 28, 2019.

- ^ "Power-On Self-Test Beep Definition - Function 1". Apple Support. February 18, 2012.

- ^ "Power On Self-Examination Beep Definition - Part 2". Apple tree Support. January 10, 2012.

- ^ a b "Almost Mac startup tones". Apple tree Support. November 8, 2018.

- ^ a b c d "A3000 Booting Problems". Archived from the original on December 3, 2019.

External links [edit]

- POST as part of the BIOS - by www.basicinputoutputsystem.com (wayback motorcar)]

- AMIBIOS8 Check Point and Beep Code List, Version 1.71 Archived 2015-08-07 at the Wayback Motorcar

- AwardBios Version 4.51PG - Postal service Codes and Mistake Messages (wayback motorcar)

- Ability poweronselftest.com - from world wide web.poweronselftest.com

- Amiga Ability On Self Test and Color Screens Schemes at Wayback Car (originally on NewTek Inc. site)

- What your Amiga is telling y'all article at Amiga History Guide

- Power On Cocky Test Beep Codes for AMI and Phoenix BIOS - from PC Hell.

- Computer Hardware - Additional information on reckoner POST / Beep Codes - from Figurer Hope.

Source: https://en.wikipedia.org/wiki/Power-on_self-test

Post a Comment for "What Is the Post (Power-on Self Test), and What Can Be Done to Troubleshoot This Process?"